PCIe从入门到精通之四:PCIe总线的拓扑结构

0. 引言

PCIe是硬件工程师跨不过去的坎。我刚开始工作就接触PCIe,工作中遇到的所有产品都有PCIe总线。在此想把自己学习PCIe的一些经历和感悟,以及踩过的坑分享在这里,与大家一起进步。所有PCIe主题的文章都会收录在《深入浅出聊PCIe》合集里,每篇文章涵盖一个PCIe的主题,预计会有几十篇文章。

在上一篇文章《PCIe从入门到精通之三:PCIe设备的内部组件》中,我们分别介绍了三类PCIe device:PCIe Root Complex、PCIe Endpoint和PCIe Switch的内部结构。在这一篇文章中我们继续介绍PCIe总线的拓扑结构。

需要下载PCIe学习资料标准的朋友(pdf格式),请关注本微信公众号"硬件工程师宝典",在对话框内回复"PCIe",将获取标准下载链接。

1. 计算机领域常见的拓扑结构

计算机网络的拓扑结构

拓扑结构是指各个设备与传输介质形成的节点与线的物理构成模式,它描述了工作节点及其之间连接的几何形状。拓扑结构的选择和设计对系统的性能、可靠性和可扩展性有重要影响。

我们比较熟悉的是计算机网络的拓扑结构,常见的网络拓扑结构主要有总线型拓扑结构(Bus Topology)、星型拓扑结构(Star Topology)、环型拓扑结构(Ring Topology)、树型拓扑结构(Tree Topology)、网状型拓扑结构(Mesh Topology)和混合型拓扑结构(Hybrid Topology)。

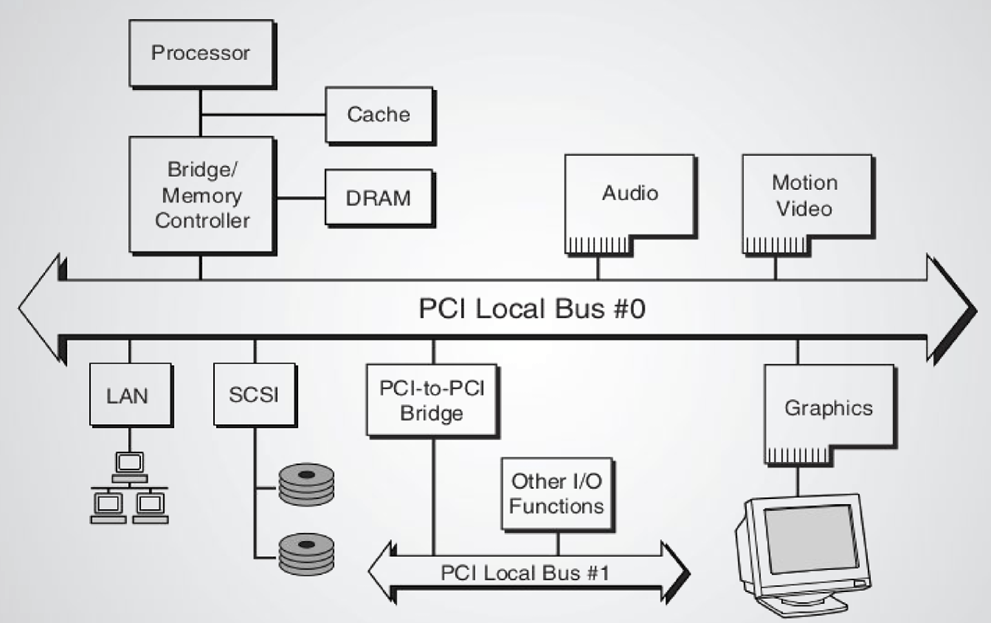

PCI总线的拓扑结构

PCI采用的是总线型拓扑结构,所有的devices都挂载在同一个PCI总线上,大家争夺资源、相互内耗、卷得太厉害了。

2. PCIe总线的拓扑结构

哪里有压迫哪里就有反抗,PCIe总线采用高速串行点对点双通道的传输架构,使得每一个所连接的设备都能够被分配到独享的通道带宽。

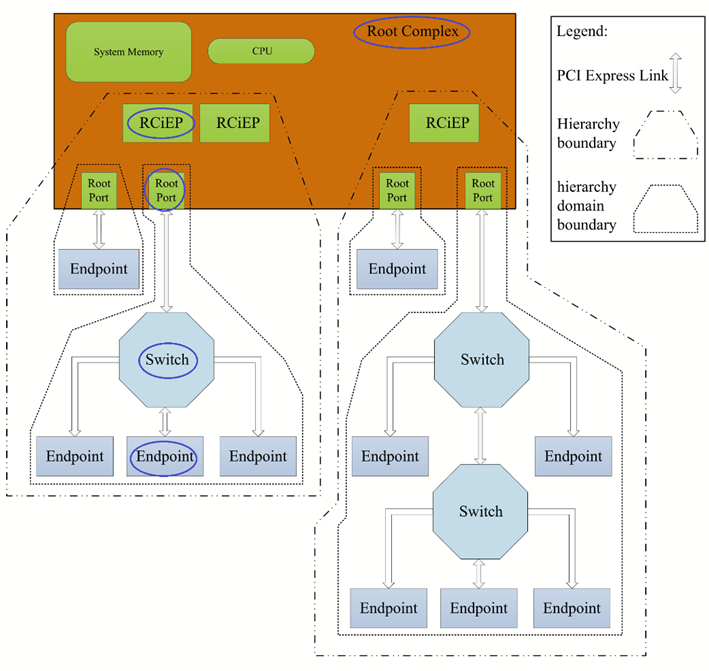

PCIe总线的拓扑结构呈树状。下图是从PCIe标准的文档里截取的PCIe拓扑结构图。把它倒过来看就像一棵树。Root port是树根,树根(Root port)通过躯干(PCIe link)向外延伸,躯干(PCIe link)的终点是Endpoint。一条链路只能挂载一个Endpoint设备,要想在一个链路上挂载多个设备必须通过PCIe switch扩展。

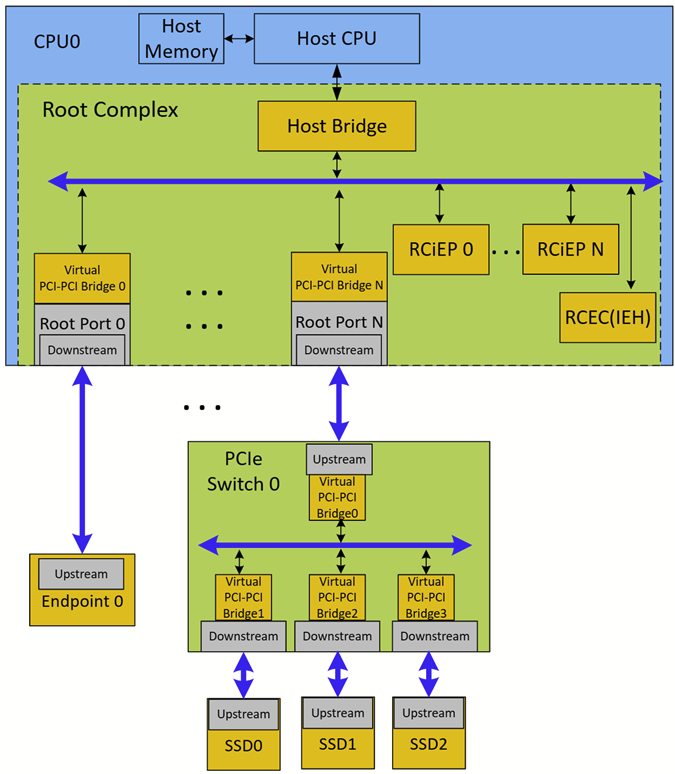

我们再次利用上一篇文章的图片,将PCI device的内部组件都展现出来。其中蓝色箭头表示PCIe Bus,每一个蓝色箭头都有一个唯一的PCIe Bus Number;黄色矩形表示PCIe Device,每个PCIe device都有自己的Device ID,Function ID和独立的配置空间;绿色虚线矩形表示Root Port,它集成在CPU内部,看不见摸不着,比较虚幻。绿色实线矩形表示PCIe switch它是一个独立于CPU的芯片,是一个可以看得见摸得着的实体。

在这棵倒立的树中,root port是树根的话,那么PCIe switch可以看作是下一级的子树根。PCIe switch有一个上游端口连接到CPU的root port;PCIe switch有若干个下游端口,这样通过不止一个下游端口从而达到了拓展PCIe总线下挂载PCIe endpoint数量的目的。

CPU是公司的CEO,Root Port是CEO的秘书办。CEO想要下面的人干点事情,都交由秘书办去安排协调。Root Port可以直接挂载Endpoint,也可以挂载Switch。对每个Switch来说,它下面的downstream port上的device,都是归它全权负责管理:upstream下来的data,它需要判断数据是传给它下面哪个设备(这就是路由),然后向下进行转发;downstream下挂载设备向Root Complex传输数据,也要通过Switch代为转发的。

3. Switch的层级有限制吗?

在PCIe的拓扑结构中,PCIe交换机(Switch)可以形成多层级(cascaded switches或switch hierarchies),以扩展PCIe设备的连接能力。

PCIe规范本身并没有对交换机层级的最大数量设置一个硬性限制。然而,实际的系统设计和性能会受到多种因素的限制,这些因素会间接限制交换机层级的深度:

-

Bus Number总数限制:同一个PCIe体系中Bus number可以有最多256个总线号(Bus Number),当使用PCIe交换机时,每个交换机每个port都会消耗一个总线号,尤其是在大型系统中,过多的层级会迅速消耗这些总线号。这是大家需要考虑的。

-

延迟和带宽:每个PCIe交换机都会引入额外的延迟,并且带宽会受到上游端口的限制。随着交换机层级的增加,数据传输的延迟会累积,并且共享带宽的效率会降低,这可能会影响系统性能,特别是对于对延迟敏感的应用(特别是最近兴起的OCP AI Server,延迟和扩展能力必须做到均衡)。

-

硬件复杂性和成本:构建多层级的PCIe交换机系统会增加硬件的复杂性、布线难度和成本。设计和实现能够支持大量设备和多层级交换的系统需要仔细考虑功耗、散热和信号完整性等问题。

-

实际应用需求:大多数消费级和企业级系统通常不需要非常深的PCIe交换机层级。例如,一些讨论中提到,为了连接大量的GPU,可能需要5-6个PCIe交换机的层级。

虽然理论上没有严格的层级限制,但在实际应用中,由于上述性能、资源和物理限制,PCIe交换机的层级深度通常是有限的。PCIe 6.0引入了分段(Segmentation)概念,使得交换机能够更智能地路由跨不同层次结构的流量,这有助于管理更复杂的PCIe拓扑。

4. 总结:PCIe拓扑结构的工作原理

PCIe拓扑结构的工作原理:

- PCIe总线使用端到端的连接方式。

- 整个PCIe系统呈现出一种树状结构,以根联合体(RC)为根,通过交换机(Switch)进行分支扩展,最终连接到各种端点(Endpoint)设备。

- CPU通过RC与PCIe设备进行通信。

- 在系统启动时,Host(CPU)会对PCIe设备进行扫描(通常采用深度优先算法),通过配置读写事务包来发现和配置下游设备,为每个设备分配资源并初始化配置空间。

这篇文章就聊到这里,敬请关注下一篇:

《PCIe从入门到精通之五:PCIe分层结构》

参考文献:

- PCI Express® Base Specification Revision 5.0 Version 1.0

- PCI Express® Base Specification Revision 6.4

- PCI Express® Base Specification Revision 7.0

需要PCIe学习资料的朋友,请关注本微信公众号"硬件工程师宝典",在对话框内回复"PCIe",将获取标准下载链接如下。